Intel Compatible, Wide Operating Range, Step-Down Controller with Internal Op Amp

## FEATURES

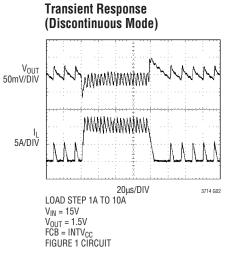

- True Current Mode with Ultrafast Transient Response

- Stable with Ceramic COUT

- t<sub>ON(MIN)</sub> < 100ns for Operation from High Input Ranges

- Supports Active Voltage Positioning

- **No Sense Resistor Required**

- 5-Bit VID Programmable Output Voltage: 0.6V to 1.75V

- **Dual N-Channel MOSFET Synchronous Drive**

- Programmable Output Offsets

- Power Good Output Voltage Monitor

- Wide VIN Range: 4V to 36V

- ±1% 0.6V Reference

- Adjustable Frequency

- Programmable Soft-Start

- **Output Overvoltage Protection**

- **Optional Short-Circuit Shutdown Timer**

- Forced Continuous Control Pin

- Logic Controlled Micropower Shutdown:  $I_0 \leq 30\mu A$

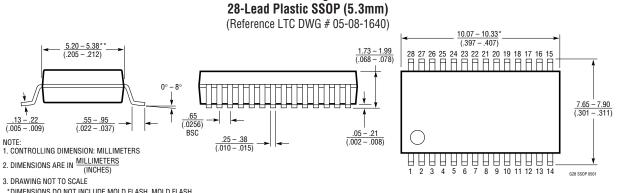

- Available in 0.209" Wide 28-Lead SSOP Package

## **APPLICATIONS**

- Power Supply for Mobile Pentium<sup>®</sup> Processors and Transmeta Processors

- Notebook and Portable Computers

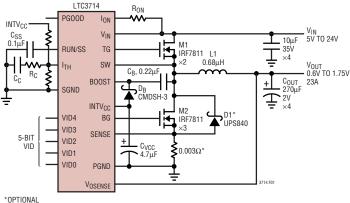

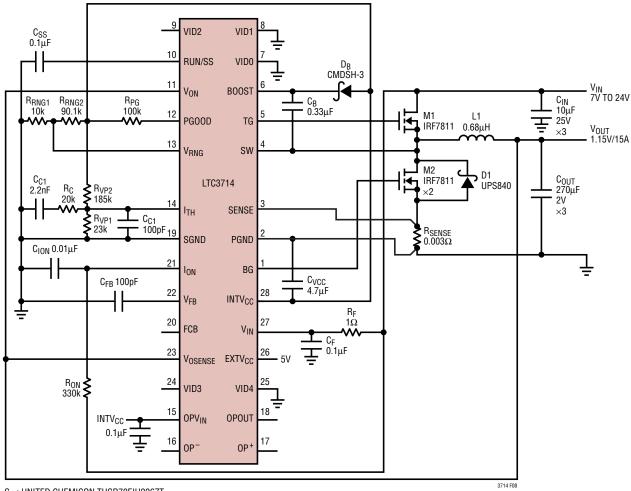

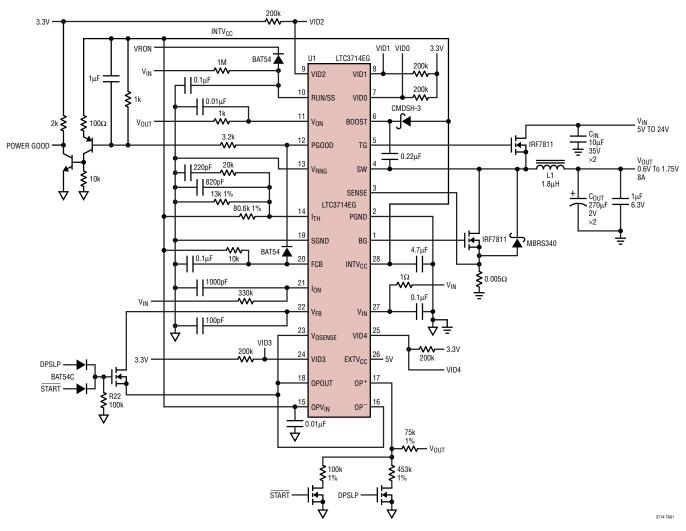

## TYPICAL APPLICATION

Figure 1. High Efficiency Step-Down Converter

# DESCRIPTION The LTC<sup>®</sup>3714 is a synchronous step-down switching

regulator controller for CPU power. An output voltage between 0.6V and 1.75V is selected by a 5-bit code (Intel mobile VID specification). The controller uses a constant on-time, valley current control architecture to deliver very low duty cycles without requiring a sense resistor. Operating frequency is selected by an external resistor and is compensated for variations in  $V_{IN}$  and  $V_{OUT}$ .

Discontinuous mode operation provides high efficiency operation at light loads. A forced continuous control pin reduces noise and RF interference and can assist secondary winding regulation by disabling discontinuous mode when the main output is lightly loaded. Internal op amp allows programmable offsets to the output voltage during power saving modes.

Fault protection is provided by internal foldback current limiting, an output overvoltage comparator and optional short-circuit shutdown timer. Soft-start capability for supply sequencing is accomplished using an external timing capacitor. The regulator current limit level is user programmable. Wide supply range allows operation from 4V to 36V at the input.

T, LTC and LT are registered trademarks of Linear Technology Corporation. Pentium is a registered trademark of Intel Corporation

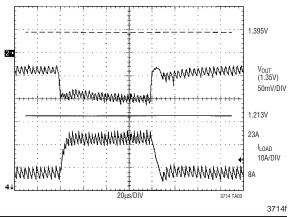

#### Transient Response of 8A to 23A Output Load Step

## **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| Input Supply Voltage ( $V_{IN}$ ), $I_{ON}$                                    |

|--------------------------------------------------------------------------------|

| (BOOST) 42V to -0.3V                                                           |

| SW, SENSE Voltages                                                             |

| EXTV <sub>CC</sub> , (BOOST – SW), RUN/SS, VID0-VID4,                          |

| PGOOD, FCB Voltages 7V to -0.3V                                                |

| $V_{ON}$ , $V_{RNG}$ Voltages (INTV <sub>CC</sub> + 0.3V) to -0.3V             |

| I <sub>TH</sub> , V <sub>FB</sub> , V <sub>OSENSE</sub> Voltages 2.7V to -0.3V |

| TG, BG, INTV <sub>CC</sub> , EXTV <sub>CC</sub> Peak Currents 2A               |

| TG, BG, INTV <sub>CC</sub> , EXTV <sub>CC</sub> RMS Currents 50mA              |

| OPV <sub>IN</sub> , OP <sup>+</sup> , OP <sup>-</sup> 0V to 18V                |

| Operating Ambient Temperature Range                                            |

| LTC3714EG (Note 2) –40°C to 85°C                                               |

| Junction Temperature (Note 3) 125°C                                            |

| Storage Temperature Range –65°C to 150°C                                       |

| Lead Temperature (Soldering, 10 sec)                                           |

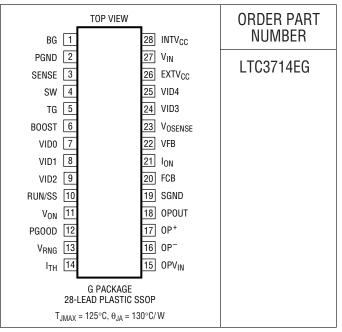

PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges.

## ELECTRICAL CHARACTERISTICS The • denotes specifications which apply over the full operating

temperature range, otherwise specifications are  $T_A = 25^{\circ}C$ .  $V_{IN} = 15V$  unless otherwise noted.

| SYMBOL                   | PARAMETER                                                    | CONDITIONS                                                                                                |   | MIN              | ТҮР               | MAX               | UNITS          |

|--------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---|------------------|-------------------|-------------------|----------------|

| Main Control Loop        |                                                              |                                                                                                           |   |                  |                   |                   |                |

| Ι <sub>Q</sub>           | Input DC Supply Current<br>Normal<br>Shutdown Supply Current |                                                                                                           |   |                  | 900<br>15         | 2000<br>30        | μΑ<br>μΑ       |

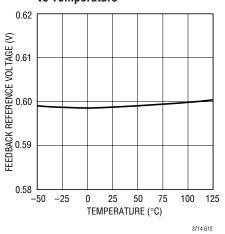

| V <sub>FB</sub>          | Feedback Reference Voltage                                   | I <sub>TH</sub> = 1.2V (Note 4)                                                                           | • | 0.594            | 0.600             | 0.606             | V              |

| $\Delta V_{FB(LINEREG)}$ | Feedback Voltage Line Regulation                             | $V_{\text{IN}}$ = 4V to 30V (Note 4), $I_{\text{TH}}$ = 1.2V                                              |   |                  | 0.002             |                   | %/V            |

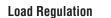

| $\Delta V_{FB(LOADREG)}$ | Feedback Voltage Load Regulation                             | I <sub>TH</sub> = 0.5V to 1.9V (Note 4)                                                                   | • |                  | -0.05             | -0.3              | %              |

| g <sub>m(EA)</sub>       | Error Amplifier Transconductance                             | I <sub>TH</sub> = 1.2V (Note 4)                                                                           | • | 1.4              | 1.7               | 2                 | ms             |

| V <sub>FCB</sub>         | Forced Continuous Threshold                                  |                                                                                                           | • | 0.57             | 0.6               | 0.63              | V              |

| I <sub>FCB</sub>         | Forced Continuous Current                                    | V <sub>FCB</sub> = 0.6V                                                                                   |   |                  | -1                | -2                | μA             |

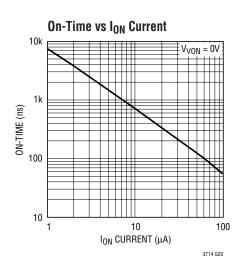

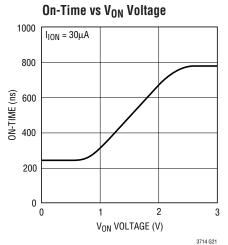

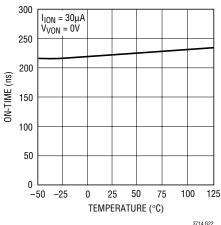

| t <sub>ON</sub>          | On-Time                                                      | I <sub>ON</sub> = 60μA, V <sub>ON</sub> = 1.5V                                                            |   | 200              | 250               | 300               | ns             |

| t <sub>ON(MIN)</sub>     | Minimum On-Time                                              | I <sub>ON</sub> = 180µA, V <sub>ON</sub> = 0V                                                             |   |                  | 50                | 100               | ns             |

| t <sub>OFF(MIN)</sub>    | Minimum Off-Time                                             | I <sub>ON</sub> = 60μA, V <sub>ON</sub> = 1.5V                                                            |   |                  | 250               | 400               | ns             |

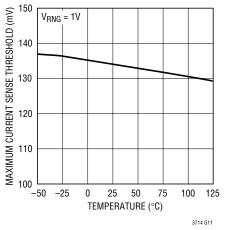

| V <sub>SENSE</sub> (MAX) | Maximum Current Sense Threshold                              | $V_{RNG} = 1V, V_{FB} = 0.56V$<br>$V_{RNG} = 0V, V_{FB} = 0.56V$<br>$V_{RNG} = INTV_{CC}, V_{FB} = 0.56V$ | • | 113<br>79<br>158 | 133<br>93<br>186  | 153<br>107<br>214 | mV<br>mV<br>mV |

| V <sub>SENSE</sub> (MIN) | Minimum Current Sense Threshold                              | $V_{RNG} = 1V, V_{FB} = 0.64V$<br>$V_{RNG} = 0V, V_{FB} = 0.64V$<br>$V_{RNG} = INTV_{CC}, V_{FB} = 0.64V$ |   |                  | -67<br>-33<br>-93 |                   | mV<br>mV<br>mV |

| $\Delta V_{FB(OV)}$      | Output Overvoltage Fault Threshold                           |                                                                                                           |   | 7.5              | 10                | 12.5              | %              |

| $\Delta V_{FB(UV)}$      | Output Undervoltage Fault Threshold                          |                                                                                                           |   | 340              | 400               | 460               | mV             |

| V <sub>RUN/SS(ON)</sub>  | RUN Pin Start Threshold                                      |                                                                                                           | • | 0.8              | 1.5               | 2                 | V              |

|                          |                                                              |                                                                                                           | 1 |                  |                   |                   | 3714f          |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes specifications which apply over the full operating temperature range, otherwise specifications are T<sub>A</sub> = 25°C. V<sub>IN</sub> = 15V unless otherwise noted.

| SYMBOL                      | PARAMETER                                              | CONDITIONS                                                    |   | MIN   | ТҮР  | MAX   | UNITS |

|-----------------------------|--------------------------------------------------------|---------------------------------------------------------------|---|-------|------|-------|-------|

| V <sub>RUN/SS(LE)</sub>     | RUN Pin Latchoff Enable Threshold                      | RUN/SS Pin Rising                                             |   |       | 4    | 4.5   | V     |

| V <sub>RUN/SS(LT)</sub>     | RUN Pin Latchoff Threshold                             | RUN/SS Pin Falling                                            |   |       | 3.5  | 4.2   | V     |

| I <sub>RUN/SS(C)</sub>      | Soft-Start Charge Current                              |                                                               |   | -0.5  | -1.2 | -3    | μA    |

| I <sub>RUN/SS(D)</sub>      | Soft-Start Discharge Current                           |                                                               |   | 0.8   | 1.8  | 3     | μA    |

| V <sub>IN(UVLO)</sub>       | Undervoltage Lockout Threshold                         | V <sub>IN</sub> Falling                                       | • |       | 3.4  | 3.9   | V     |

| V <sub>IN(UVLOR)</sub>      | Undervoltage Lockout Threshold                         | V <sub>IN</sub> Rising                                        | • |       | 3.5  | 4     | V     |

| TG R <sub>UP</sub>          | TG Driver Pull-Up On Resistance                        | TG High                                                       |   |       | 2    | 3     | Ω     |

| TG R <sub>DOWN</sub>        | TG Driver Pull-Down On Resistance                      | TG Low                                                        |   |       | 2    | 3     | Ω     |

| BG R <sub>UP</sub>          | BG Driver Pull-Up On Resistance                        | BG High                                                       |   |       | 3    | 4     | Ω     |

| BG R <sub>DOWN</sub>        | BG Driver Pull-Down On Resistance                      | BG Low                                                        |   |       | 1    | 2     | Ω     |

| TG t <sub>r</sub>           | TG Rise Time                                           | C <sub>LOAD</sub> = 3300pF                                    |   |       | 20   |       | ns    |

| TG t <sub>f</sub>           | TG Fall Time                                           | C <sub>LOAD</sub> = 3300pF                                    |   |       | 20   |       | ns    |

| BG t <sub>r</sub>           | BG Rise Time                                           | C <sub>LOAD</sub> = 3300pF                                    |   |       | 20   |       | ns    |

| BG t <sub>f</sub>           | BG Fall Time                                           | C <sub>LOAD</sub> = 3300pF                                    |   |       | 20   |       | ns    |

| Internal V <sub>CC</sub> Re | gulator                                                |                                                               | ľ |       |      |       |       |

| VINTVCC                     | Internal V <sub>CC</sub> Voltage                       | $6V < V_{IN} < 30V, V_{EXTVCC} = 4V$                          | • | 4.7   | 5    | 5.3   | V     |

| $\Delta V_{LDO(LOADREG)}$   | Internal V <sub>CC</sub> Load Regulation               | I <sub>CC</sub> = 0mA to 20mA, V <sub>EXTVCC</sub> = 4V       |   |       | -0.1 | ±2    | %     |

| V <sub>EXTVCC</sub>         | EXTV <sub>CC</sub> Switchover Voltage                  | I <sub>CC</sub> = 20mA, V <sub>EXTVCC</sub> Rising            | • | 4.5   | 4.7  |       | V     |

| $\Delta V_{\text{EXTVCC}}$  | EXTV <sub>CC</sub> Switch Drop Voltage                 | $I_{CC} = 20 \text{mA}, V_{EXTVCC} = 5 \text{V}$              |   |       | 150  | 300   | mV    |

| $\Delta V_{EXTVCC(HYS)}$    | EXTV <sub>CC</sub> Switchover Hysteresis               |                                                               |   |       | 200  |       | mV    |

| PGOOD Output                | ·                                                      |                                                               |   |       |      |       | ·     |

| $\Delta V_{\text{FBH}}$     | PGOOD Upper Threshold                                  | V <sub>FB</sub> Rising                                        |   | 7.5   | 10   | 12.5  | %     |

| $\Delta V_{FBL}$            | PGOOD Lower Threshold                                  | V <sub>FB</sub> Falling                                       |   | -7.5  | -10  | -12.5 | %     |

| $\Delta V_{FB(HYS)}$        | PGOOD Hysteresis                                       | V <sub>FB</sub> Returning                                     |   |       | 1    | 2.5   | %     |

| V <sub>PGL</sub>            | PGOOD Low Voltage                                      | I <sub>PGOOD</sub> = 1mA                                      |   |       | 0.15 | 0.4   | V     |

| VID DAC                     |                                                        |                                                               |   |       |      |       |       |

| V <sub>VID(T)</sub>         | VID0-VID4 Logic Threshold Voltage                      |                                                               |   | 0.4   | 1.2  | 2     | V     |

| I <sub>VID(PULLUP)</sub>    | VID0-VID4 Pull-Up Current                              | $V_{VID0}$ to $V_{VID4} = 0V$                                 |   |       | -2.5 |       | μA    |

| V <sub>VID(PULLUP)</sub>    | VID0-VID4 Pull-Up Voltage                              | V <sub>VID0</sub> to V <sub>VID4</sub> Open                   |   |       | 4.5  |       | V     |

| I <sub>VID(LEAK)</sub>      | VID0-VID4 Leakage Current                              | $V_{VID0}$ to $V_{VID4}$ = 5V, $V_{RUN/SS}$ = 0V              |   |       | 0.01 | 1     | μA    |

| R <sub>VID</sub>            | Resistance from V <sub>OSENSE</sub> to V <sub>FB</sub> |                                                               |   | 6     | 10   | 14    | KΩ    |

| $\Delta V_{OSENSE}$         | DAC Output Accuracy                                    | V <sub>OSENSE</sub> Programmed from<br>0.6V to 1.75V (Note 5) |   | -0.45 | 0    | 0.25  | %     |

#### $V_{\text{IN}} = 5V$ unless otherwise noted.

| Internal Op Amp |                             |  |  |           |      |          |  |

|-----------------|-----------------------------|--|--|-----------|------|----------|--|

| V <sub>OS</sub> | Input Offset Voltage        |  |  | 400       | 1000 | μV       |  |

| l <sub>OS</sub> | Input Offset Current        |  |  | 4         | 10   | nA       |  |

| I <sub>B</sub>  | Input Bias Current          |  |  | 45        | 80   | nA       |  |

| CMRR            | Common Mode Rejection Ratio |  |  | 100<br>80 |      | dB<br>dB |  |

## **ELECTRICAL CHARACTERISTICS** The • denotes specifications which apply over the full operating

temperature range, otherwise specifications are  $T_A = 25^{\circ}C$ .  $V_{IN} = 5V$  unless otherwise noted.

| SYMBOL           | PARAMETER                    | CONDITIONS                                             |   | MIN | ТҮР      | MAX | UNITS    |

|------------------|------------------------------|--------------------------------------------------------|---|-----|----------|-----|----------|

| PSRR             | Power Supply Rejection Ratio | $OPV_{IN} = 3V$ to 12.5V, $OP_{OUT} = V_0 = 1V$        |   |     | 100      |     | dB       |

| A <sub>VOL</sub> | Large-Signal Voltage Gain    | $OPV_{IN} = 5V, OP_{OUT} = 500mV$ to 4.5V, $R_L = 10k$ |   |     | 1500     |     | V/mV     |

| V <sub>OL</sub>  | Output Voltage Swing LOW     | OPV <sub>IN</sub> = 5V, I <sub>SINK</sub> = 5mA        | • |     | 165      | 500 | mV       |

| V <sub>OH</sub>  | Output Voltage Swing HIGH    | OPV <sub>IN</sub> = 5V, I <sub>SOURCE</sub> = 5mA      | • | 4.5 | 4.87     |     | V        |

| I <sub>SC</sub>  | Short-Circuit Current        | Short to GND<br>Short to OPV <sub>IN</sub>             |   |     | 30<br>40 |     | mA<br>mA |

| ls               | Supply Current               |                                                        |   |     | 170      | 300 | μA       |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** The LTC3714E is guaranteed to meet performance specifications from 0°C to 70°C. Specifications over the -40°C to 85°C operating temperature range are assured by design, characterization and correlation with statistical process controls.

**Note 4:** The LTC3714 is tested in a feedback loop that adjusts  $V_{FB}$  to achieve a specified error amplifier output voltage ( $I_{TH}$ ).

Note 5: The LTC3714 VID DAC is tested in a feedback loop that adjusts  $V_{OSENSE}$  to achieve a specified feedback voltage (V\_{FB} = 0.6V) for each DAC VID code.

Note 3:  $T_J$  is calculated from the ambient temperature  $T_A$  and power dissipation  $\mathsf{P}_D$  as follows:

LTC3714EG:  $T_J = T_A + (P_D \bullet 130^{\circ}C/W)$

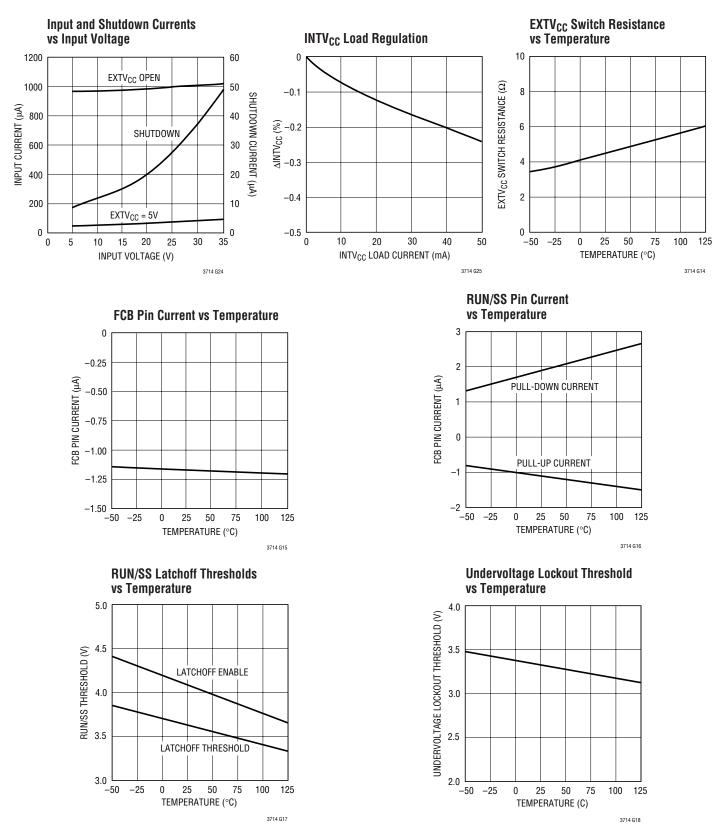

## **TYPICAL PERFORMANCE CHARACTERISTICS**

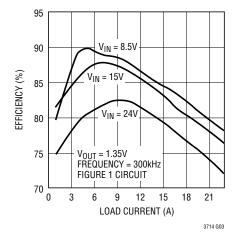

#### **Efficiency vs Load Current**

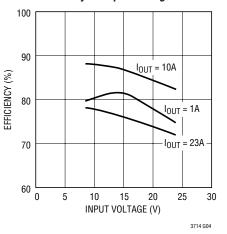

#### **Efficiency vs Input Voltage**

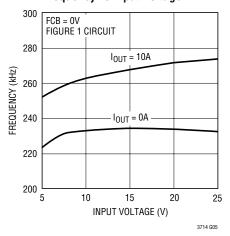

#### **Frequency vs Input Voltage**

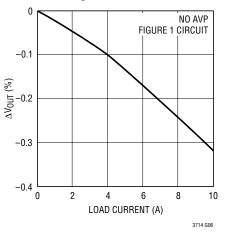

#### I<sub>TH</sub> Voltage vs Load Current

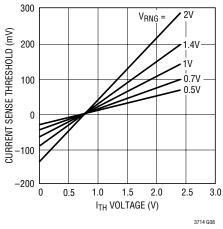

#### Current Sense Threshold vs I<sub>TH</sub> Voltage

## TYPICAL PERFORMANCE CHARACTERISTICS

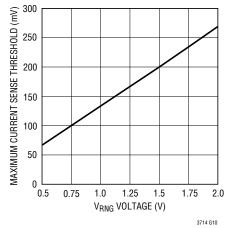

Maximum Current Sense Threshold vs V<sub>RNG</sub> Voltage

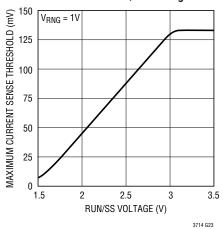

Maximum Current Sense Threshold vs RUN/SS Voltage

Maximum Current Sense Threshold vs Temperature

Feedback Reference Voltage vs Temperature

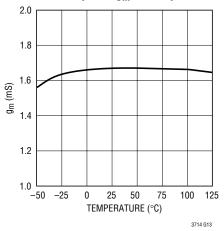

Error Amplifier g<sub>m</sub> vs Temperature

## TYPICAL PERFORMANCE CHARACTERISTICS

## PIN FUNCTIONS

**BG (Pin 1):** Bottom Gate Drive. Drives the gate of the bottom N-channel MOSFET between ground and  $INTV_{CC}$ .

**PGND (Pin 2):** Power Ground. Connect this pin closely to the bottom of the sense resistor or if no sense resistor is used, to the source of the bottom N-channel MOSFET, the (-) terminal of C<sub>VCC</sub> and the (-) terminal of C<sub>IN</sub>.

**SENSE (Pin 3):** Current Sense Comparator Input. The (+) input to the current comparator is normally connected to the SW node unless using a sense resistor (see Applications Information).

**SW (Pin 4):** Switch Node. The (–) terminal of the bootstrap capacitor  $C_B$  connects here. This pin swings from a diode voltage drop below ground up to  $V_{IN}$ .

**TG (Pin 5):** Top Gate Drive. Drives the top N-channel MOSFET with a voltage swing equal to  $INTV_{CC}$  superimposed on the switch node voltage SW.

**BOOST (Pin 6):** Boosted Floating Driver Supply. The (+) terminal of the bootstrap capacitor  $C_B$  connects here. This pin swings from a diode voltage drop below INTV<sub>CC</sub> up to  $V_{IN}$  + INTV<sub>CC</sub>.

**VID0-VID4 (Pins 7, 8, 9, 24, 25):** VID Digital Inputs. The voltage identification (VID) code sets the internal feedback resistor divider ratio for different output voltages as shown in Table 1. If unconnected, the pins are pulled high by internal  $2.5\mu$ A current sources.

**RUN/SS (Pin 10):** Run Control and Soft-Start Input. A capacitor to ground at this pin sets the ramp time to full output current (approximately  $3s/\mu F$ ) and the time delay for overcurrent latchoff (see Applications Information). Forcing this pin below 0.8V shuts down the device.

$V_{ON}$  (Pin 11): On-Time Voltage Input. Voltage trip point for the on-time comparator. Tying this pin to the output voltage makes the on-time proportional to  $V_{OUT}$ . The comparator input defaults to 0.7V when the pin is grounded, 2.4V when the pin is tied to  $INTV_{CC}$ .

**PGOOD (Pin 12):** Power Good Output. Open drain logic output that is pulled to ground when the output voltage is not within  $\pm 10\%$  of the regulation point.

$V_{RNG}$  (Pin 13): Sense Voltage Range Input. The voltage at this pin is ten times the nominal sense voltage at maxi-

mum output current and can be set from 0.5V to 2V by a resistive divider from  $INTV_{CC}$ . The sense voltage defaults to 70mV when this pin is tied to ground, 140mV when tied to  $INTV_{CC}$ .

**I<sub>TH</sub> (Pin 14):** Current Control Threshold and Error Amplifier Compensation Point. The current comparator threshold increases with this control voltage. The voltage ranges from 0V to 2.4V with 0.8V corresponding to zero sense voltage (zero current).

$OPV_{IN}$  (Pin 15): Internal Op Amp Supply. Connect to INTV<sub>CC</sub> or a separate supply greater than 5V.

**OP<sup>-</sup> (Pin 16):** Negative Input of the Internal Op Amp.

**OP+ (Pin 17):** Positive Input of the Internal Op Amp.

**OPOUT (Pin 18):** Output of the Internal Op Amp.

**SGND (Pin 19):** Signal Ground. All small-signal components and compensation components should connect to this ground, which in turn connects to PGND at one point.

**FCB (Pin 20):** Forced Continous Input. Tie this pin to ground to force continuous synchronous operation at low load, to  $INTV_{CC}$  to enable discontinuous mode operation at low load or to a resistive divider from a secondary output when using a secondary winding.

$I_{ON}$  (Pin 21): On-Time Current Input. Tie a resistor from  $V_{IN}$  to this pin to set the one-shot timer current and thereby set the switching frequency.

$V_{FB}$  (Pin 22): Error Amplifier Feedback Input. This pin connects to both the error amplifier input and to the output of the internal resistive divider. It can be used to attach additional compensation components if desired.

**V**<sub>OSENSE</sub> (**Pin 23**): Output Voltage Sense. The output voltage connects here to the input of the internal resistive feedback divider.

**EXTV<sub>CC</sub> (Pin 26):** External V<sub>CC</sub> Input. When EXTV<sub>CC</sub> exceeds 4.7V, an internal switch connects this pin to INTV<sub>CC</sub> and shuts down the internal regulator so that controller and gate drive power is drawn from EXTV<sub>CC</sub>. Do not exceed 7V at this pin and ensure that EXTV<sub>CC</sub> <  $V_{IN}$ .

$V_{IN}$  (Pin 27): Main Input Supply. Decouple this pin to SGND with an RC filter (1 $\Omega$ , 0.1 $\mu$ F).

### PIN FUNCTIONS

**INTV<sub>CC</sub> (Pin 28):** Internal 5V Regulator Output. The driver and control circuits are powered from this voltage. De-

couple this pin to power ground with a minimum of  $4.7\mu F$  tantalum or other low ESR capacitor.

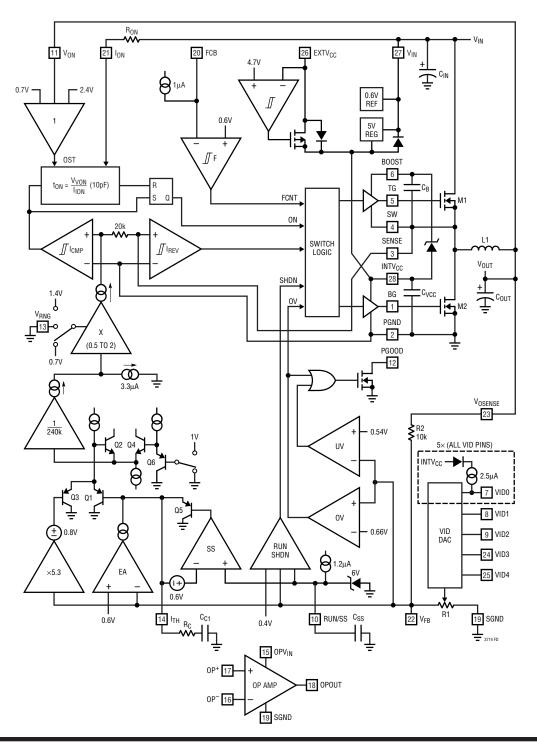

### FUNCTIONAL DIAGRAM

T LINEAR TECHNOLOGY

## OPERATION

#### Main Control Loop

The LTC3714 is a constant on-time, current mode controller for DC/DC step-down converters. In normal operation, the top MOSFET is turned on for a fixed interval determined by a one-shot timer OST. When the top MOSFET is turned off, the bottom MOSFET is turned on until the current comparator I<sub>CMP</sub> trips, restarting the one-shot timer and initiating the next cycle. Inductor current is determined by sensing the voltage between the PGND and SENSE pins using either the bottom MOSFET on-resistance or a separate sense resistor. The voltage on the  $I_{TH}$ pin sets the comparator threshold corresponding to inductor valley current. The error amplifier EA adjusts this voltage by comparing the feedback signal V<sub>FB</sub> from the output voltage with an internal 0.6V reference. The feedback voltage is derived from the output voltage by a resistive divider DAC that is set by the VID code pins VID0-VID4. If the load current increases, it causes a drop in the feedback voltage relative to the reference. The  $I_{TH}$  voltage then rises until the average inductor current again matches the load current.

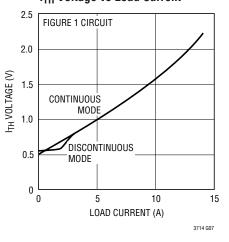

At low load currents, the inductor current can drop to zero and become negative. This is detected by current reversal comparator  $I_{REV}$  which then shuts off M2, resulting in discontinuous operation. Both switches will remain off with the output capacitor supplying the load current until the  $I_{TH}$  voltage rises above the zero current level (0.8V) to initiate another cycle. Continuous synchronous operation can be forced in the LTC3714 by bringing the FCB pin below 0.6V. The benefit of forced continuous operation is lower output voltage ripple, faster transient response to current load steps and a much quieter frequency spectrum so that it won't interfere with any neighboring noise sensitive components. The operating frequency is determined implicitly by the top MOSFET on-time and the duty cycle required to maintain regulation. The one-shot timer generates an on-time that is proportional to the ideal duty cycle, thus holding frequency approximately constant with changes in  $V_{IN}$  and  $V_{OUT}$ . The nominal frequency can be adjusted with an external resistor  $R_{ON}$ .

Overvoltage and undervoltage comparators OV and UV pull the PGOOD output low if the output feedback voltage exits  $a \pm 10\%$  window around the regulation point. Furthermore, in an overvoltage condition, M1 is turned off and M2 is turned on and held on until the overvoltage condition clears.

Foldback current limiting is provided if the output is shorted to ground. As  $V_{FB}$  drops, the buffered current threshold voltage  $I_{THB}$  is pulled down by clamp Q3 to a 1V level set by Q2 and Q6. This reduces the inductor valley current level to one sixth of its maximum value as  $V_{FB}$  approaches ground.

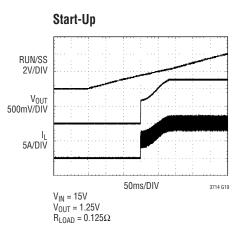

Pulling the RUN/SS pin low forces the controller into its shutdown state, turning off both M1 and M2. Releasing the pin allows an internal  $1.2\mu$ A current source to charge up an external soft-start capacitor C<sub>SS</sub>. When this voltage reaches 1.5V, the controller turns on and begins switching, but with the I<sub>TH</sub> voltage clamped at approximately 0.6V below the RUN/SS voltage. As C<sub>SS</sub> continues to charge, the soft-start current limit is removed.

## OPERATION

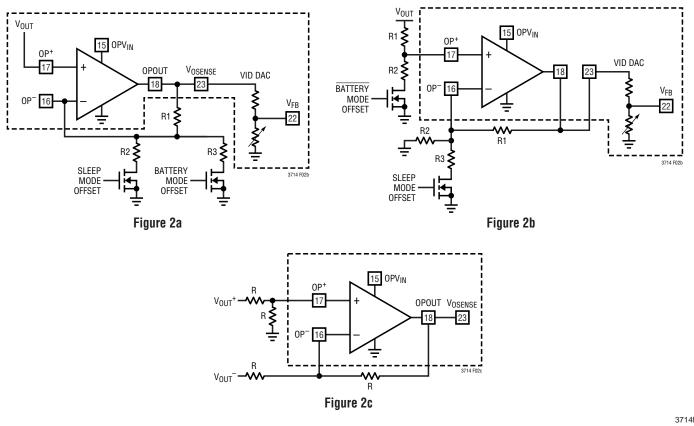

#### Internal Op Amp

The internal op amp allows the user to program accurate offsets to the output voltage during power saving modes. By connecting the OP<sup>+</sup> pin to the output, the OPOUT pin to the V<sub>OSENSE</sub> pin and an external resistor R1 between the OP<sup>-</sup>and OPOUT pins, the op amp is hooked up as a unitygain feedback amplifier. Resistors R2 and R3, together with series switches, can then be placed on the OP<sup>-</sup> pin to allow negative offsets to be switched onto the output voltage (see Figures 2a and 2b). The accuracy of the offset will depend on the matching of the external resistors R1 to R2 and R3.\*

For applications that require less accurate output offsets, or none at all, the user can use the internal op amp for true differential remote sensing of the output voltage by connecting OPOUT to  $V_{OSENSE}$  and using OP<sup>+</sup> and OP<sup>-</sup> for differential sensing across the output capacitor as shown in Figure 2c.

#### INTV<sub>CC</sub>/EXTV<sub>CC</sub> Power

Power for the top and bottom MOSFET drivers and most of the internal controller circuitry is derived from the INTV<sub>CC</sub> pin. The top MOSFET driver is powered from a floating bootstrap capacitor C<sub>B</sub>. This capacitor is recharged from INTV<sub>CC</sub> through an external Schottky diode  $D_B$  when the top MOSFET is turned off. When the EXTV<sub>CC</sub> pin is grounded, an internal 5V low dropout regulator supplies the  $INTV_{CC}$  power from  $V_{IN}$ . If  $EXTV_{CC}$  rises above 4.7V, the internal regulator is turned off, and an internal switch connects EXTV<sub>CC</sub> to INTV<sub>CC</sub>. This allows a high efficiency source connected to EXTV<sub>CC</sub>, such as an external 5V supply or a secondary output from the converter, to provide the INTV<sub>CC</sub> power. Voltages up to 7V can be applied to EXTV<sub>CC</sub> for additional gate drive. If the input voltage is low and INTV<sub>CC</sub> drops below 3.5V, undervoltage lockout circuitry prevents the power switches from turning on.

\*An alternate configuration, shown in Figure 2b, can be used to program offsets as well. Either configuration can be used, depending upon the logic of control signals. If offsets are not required, the op amp can be used to remotely sense the output voltage, proving true differential sense.

The basic LTC3714 application circuit is shown in Figure 1. External component selection is primarily determined by the maximum load current and begins with the selection of the sense resistance and power MOSFET switches. The LTC3714 can use either a sense resistor or the on-resistance of the synchronous power MOSFET for determining the inductor current. The desired amount of ripple current and operating frequency largely determines the inductor value. Finally,  $C_{\rm IN}$  is selected for its ability to handle the large RMS current into the converter and  $C_{\rm OUT}$  is chosen with low enough ESR to meet the output voltage ripple and transient specification.

#### Maximum Sense Voltage and $V_{\mbox{RNG}}$ Pin

Inductor current is determined by measuring the voltage across a sense resistance that appears between the PGND and SENSE pins. The maximum sense voltage is set by the voltage applied to the  $V_{RNG}$  pin and is equal to approximately (0.133) $V_{RNG}$ . The current mode control loop will not allow the inductor current valleys to exceed (0.133) $V_{RNG}/R_{SENSE}$ . In practice, one should allow some margin for variations in the LTC3714 and external component values and a good guide for selecting the sense resistance is:

$$R_{\text{SENSE}} = \frac{V_{\text{RNG}}}{10 \bullet I_{\text{OUT}(\text{MAX})}}$$

An external resistive divider from  $INTV_{CC}$  can be used to set the voltage of the  $V_{RNG}$  pin between 0.5V and 2V resulting in nominal sense voltages of 50mV to 200mV. Additionally, the  $V_{RNG}$  pin can be tied to SGND or  $INTV_{CC}$ in which case the nominal sense voltage defaults to 70mV or 140mV, respectively. The maximum allowed sense voltage is about 1.33 times this nominal value.

#### Connecting the SENSE Pin

The LTC3714 can be used with or without a sense resistor. When using a sense resistor, it is placed between the source of the bottom MOSFET M2 and ground. Connect the SENSE pin to the source of the bottom MOSFET so that the resistor appears between the SENSE and PGND pins. Using a sense resistor provides a well defined current limit, but adds cost and reduces efficiency. Alternatively, one can eliminate the sense resistor and use the bottom MOSFET as the current sense element by simply connecting the SENSE pin to the switch node SW at the drain of the bottom MOSFET. This improves efficiency, but one must carefully choose the MOSFET on-resistance as discussed below.

#### **Power MOSFET Selection**

The LTC3714 requires two external N-channel power MOSFETs, one for the top (main) switch and one for the bottom (synchronous) switch. Important parameters for the power MOSFETs are the breakdown voltage  $V_{(BR)DSS}$ , threshold voltage  $V_{(GS)TH}$ , on-resistance  $R_{DS(ON)}$ , reverse transfer capacitance  $C_{RSS}$  and maximum current  $I_{DS(MAX)}$ .

The gate drive voltage is set by the 5V  $INTV_{CC}$  supply. Consequently, logic-level threshold MOSFETs must be used in LTC3714 applications. If the input voltage is expected to drop below 5V, then sub-logic level threshold MOSFETs should be considered.

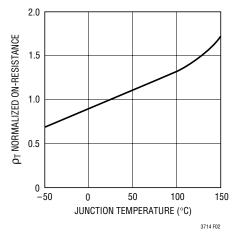

When the bottom MOSFET is used as the current sense element, particular attention must be paid to its on-resistance. MOSFET on-resistance is typically specified with a maximum value  $R_{DS(ON)(MAX)}$  at 25°C. In this case, additional margin is required to accommodate the rise in MOSFET on-resistance with temperature:

$$R_{DS(ON)(MAX)} = \frac{R_{SENSE}}{\rho_{T}}$$

The  $\rho_T$  term is a normalization factor (unity at 25°C) accounting for the significant variation in on-resistance with temperature, typically about 0.4%/°C as shown in Figure 3. Junction-to-case temperature is about 30°C in most applications. For a maximum ambient temperature of 70°C, using a value  $\rho_{100°C} = 1.3$  is reasonable.

The power dissipated by the top and bottom MOSFETs strongly depends upon their respective duty cycles and the load current. When the LTC3714 is operating in continuous mode, the duty cycles for the MOSFETs are:

$$\begin{split} D_{TOP} &= \frac{V_{OUT}}{V_{IN}} \\ D_{BOT} &= \frac{V_{IN} - V_{OUT}}{V_{IN}} \end{split}$$

Figure 3. R<sub>DS(ON)</sub> vs Temperature

The resulting power dissipation in the MOSFETs at maximum output current are:

$P_{BOT} = D_{BOT} I_{OUT(MAX)}^2 \rho_{T(BOT)} R_{DS(ON)(MAX)}$

Both MOSFETs have  $I^2R$  losses and the top MOSFET includes an additional term for transition losses, which are largest at high input voltages. The constant k =  $1.7A^{-1}$  can be used to estimate the amount of transition loss. The bottom MOSFET losses are greatest when the bottom duty cycle is near 100%, during a short-circuit or at high input voltage.

#### **Operating Frequency**

The choice of operating frequency is a tradeoff between efficiency and component size. Low frequency operation improves efficiency by reducing MOSFET switching losses but requires larger inductance and/or capacitance in order to maintain low output ripple voltage.

The operating frequency of LTC3714 applications is determined implicitly by the one-shot timer that controls the on-time  $t_{ON}$  of the top MOSFET switch. The on-time is set by the current into the  $I_{ON}$  pin and the voltage at the  $V_{ON}$  pin according to:

$$t_{ON} = \frac{V_{VON}}{I_{ION}} (10 \text{pF})$$

TECHNOLOGY

Tying a resistor  $R_{ON}$  from  $V_{IN}$  to the  $I_{ON}$  pin yields an ontime inversely proportional to  $V_{IN}$ . For a step-down converter, this results in approximately constant frequency operation as the input supply varies:

$$f = \frac{V_{OUT}}{V_{VON}R_{ON}(10pF)}$$

To hold frequency constant during output voltage changes, tie the  $V_{ON}$  pin to  $V_{OUT}$ . The  $V_{ON}$  pin has internal clamps that limit its input to the one-shot timer. If the pin is tied below 0.7V, the input to the one-shot is clamped at 0.7V. Similarly, if the pin is tied above 2.4V, the input is clamped at 2.4V.

Because the voltage at the  $I_{ON}$  pin is about 0.7V, the current into this pin is not exactly inversely proportional to  $V_{IN}$ , especially in applications with lower input voltages. To correct for this error, an additional resistor  $R_{ON2}$  connected from the  $I_{ON}$  pin to the 5V INTV<sub>CC</sub> supply will further help to stabilize the frequency.

$$\mathsf{R}_{\mathsf{ON2}} = \frac{5\mathsf{V}}{0.7\mathsf{V}}\mathsf{R}_{\mathsf{ON}}$$

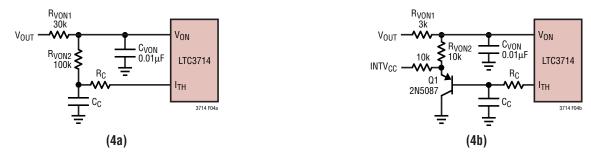

Changes in the load current magnitude will also cause frequency shift. Parasitic resistance in the MOSFET switches and inductor reduce the effective voltage across the inductance, resulting in increased duty cycle as the load current increases. By lengthening the on-time slightly as current increases, constant frequency operation can be maintained. This is accomplished with a resistive divider from the  $I_{TH}$  pin to the  $V_{ON}$  pin and  $V_{OUT}$ . The values required will depend on the parasitic resistances in the specific application. A good starting point is to feed about 25% of the voltage change at the  $I_{TH}$  pin to the  $V_{ON}$  pin as shown in Figure 4a. Place capacitance on the V<sub>ON</sub> pin to filter out the  $I_{TH}$  variations at the switching frequency. The resistor load on  $I_{TH}$  reduces the DC gain of the error amp and degrades load regulation, which can be avoided by using the PNP emitter follower of Figure 4b.

Figure 4. Correcting Frequency Shift with Load Current Changes

#### Inductor Selection

Given the desired input and output voltages, the inductor value and operating frequency determine the ripple current:

$$\Delta I_{L} = \left(\frac{V_{OUT}}{fL}\right) \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

Lower ripple current reduces cores losses in the inductor, ESR losses in the output capacitors and output voltage ripple. Highest efficiency operation is obtained at low frequency with small ripple current. However, achieving this requires a large inductor. There is a tradeoff between component size, efficiency and operating frequency.

A reasonable starting point is to choose a ripple current that is about 40% of  $I_{OUT(MAX)}$ . The largest ripple current occurs at the highest  $V_{IN}$ . To guarantee that ripple current does not exceed a specified maximum, the inductance should be chosen according to:

$$L = \left(\frac{V_{OUT}}{f\Delta I_{L(MAX)}}\right) \left(1 - \frac{V_{OUT}}{V_{IN(MAX)}}\right)$$

Once the value for L is known, the type of inductor must be selected. A variety of inductors designed for high current, low voltage applications are available from manufacturers such as Sumida and Panasonic.

#### Schottky Diode D1 Selection

The Schottky diode D1 shown in Figure 1 conducts during the dead time between the conduction of the power MOSFET switches. It is intended to prevent the body diode of the bottom MOSFET from turning on and storing charge during the dead time, causing a modest (about 1%) efficiency loss. The diode can be rated for about one half to one fifth of the full load current since it is on for only a fraction of the duty cycle. In order for the diode to be effective, the inductance between it and the bottom MOSFET must be as small as possible, mandating that these components be placed adjacently. The diode can be omitted if the efficiency loss is tolerable.

#### $C_{\text{IN}}$ and $C_{\text{OUT}}$ Selection

The input capacitance  $C_{IN}$  is required to filter the square wave current at the drain of the top MOSFET. Use a low ESR capacitor sized to handle the maximum RMS current.

$$I_{RMS} \cong I_{OUT(MAX)} \frac{V_{OUT}}{V_{IN}} \sqrt{\frac{V_{IN}}{V_{OUT}} - 1}$$

This formula has a maximum at  $V_{IN} = 2V_{OUT}$ , where  $I_{RMS} = I_{OUT(MAX)}/2$ . This simple worst-case condition is commonly used for design because even significant deviations do not offer much relief. Note that ripple current ratings from capacitor manufacturers are often based on only 2000 hours of life which makes it advisable to derate the capacitor.

The selection of C<sub>OUT</sub> is primarily determined by the ESR required to minimize voltage ripple and load step transients. The output ripple  $\Delta V_{OUT}$  is approximately bounded by:

$$\Delta V_{OUT} \le \Delta I_L \left( \text{ESR} + \frac{1}{8 \text{fC}_{OUT}} \right)$$

Since  $\Delta I_L$  increases with input voltage, the output ripple is highest at maximum input voltage. Typically, once the ESR requirement is satisfied, the capacitance is adequate for filtering and has the necessary RMS current rating.

Multiple capacitors placed in parallel may be needed to meet the ESR and RMS current handling requirements. Dry tantalum, special polymer, POSCAP aluminum electrolytic and ceramic capacitors are all available in surface mount packages. Special polymer capacitors offer very low ESR but have lower capacitance density than other types. Tantalum capacitors have the highest capacitance density but it is important to only use types that have been surge tested for use in switching power supplies. Aluminum electrolytic capacitors have significantly higher ESR, but can be used in cost-sensitive applications providing that consideration is given to ripple current ratings and long term reliability. Ceramic capacitors have excellent low ESR characteristics but can have a high voltage coefficient and audible piezoelectric effects. The high Q of ceramic capacitors with trace inductance can also lead to significant ringing. When used as input capacitors, care must be taken to ensure that ringing from inrush currents and switching does not pose an overvoltage hazard to the power switches and controller. High performance throughhole capacitors may also be used, but an additional ceramic capacitor in parallel is recommended to reduce the effect of their lead inductance.

#### Top MOSFET Driver Supply (C<sub>B</sub>, D<sub>B</sub>)

An external bootstrap capacitor  $C_B$  connected to the BOOST pin supplies the gate drive voltage for the topside MOSFET. This capacitor is charged through diode  $D_B$  from INTV<sub>CC</sub> when the switch node is low. When the top MOSFET turns on, the switch node rises to  $V_{IN}$  and the BOOST pin rises to approximately  $V_{IN}$  + INTV<sub>CC</sub>. The boost capacitor needs

to store about 100 times the gate charge required by the top MOSFET. In most applications  $0.1\mu F$  to  $0.47\mu F$  is adequate.

#### **Discontinuous Mode Operation and FCB Pin**

The FCB pin determines whether the bottom MOSFET remains on when current reverses in the inductor. Tying this pin above its 0.6V threshold (typically to  $INTV_{CC}$ ) enables discontinuous operation where the bottom MOSFET turns off when inductor current reverses. The load current at which current reverses and discontinuous operation begins, depends on the amplitude of the inductor ripple current. The ripple current depends on the choice of inductor value and operating frequency as well as the input and output voltages.

Tying the FCB pin below the 0.6V threshold forces continuous synchronous operation, allowing current to reverse at light loads.

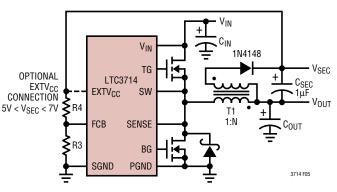

In addition to providing a logic input to force continuous operation, the FCB pin provides a means to maintain a flyback winding output when the primary is operating in discontinuous mode. The secondary output  $V_{SEC}$  is normally set as shown in Figure 5 by the turns ratio N of the transformer. However, if the controller goes into discontinuous mode and halts switching due to a light primary load current, then  $V_{SEC}$  will droop. An external resistor divider from  $V_{SEC}$  to the FCB pin sets a minimum voltage  $V_{SEC(MIN)}$  below which continuous operation is forced until  $V_{SEC}$  has risen above its minimum.

$$V_{\text{SEC(MIN)}} = 0.6V \left(1 + \frac{\text{R4}}{\text{R3}}\right)$$

#### Fault Conditions: Current Limit and Foldback

The maximum inductor current is inherently limited in a current mode controller by the maximum sense voltage. In the LTC3714, the maximum sense voltage is controlled by the voltage on the  $V_{RNG}$  pin. With valley current control, the maximum sense voltage and the sense resistance determine the maximum allowed inductor valley current. The corresponding output current limit is:

$$I_{LIMIT} = \frac{V_{SNS(MAX)}}{*R_{DS(ON)}\rho_T} + \frac{1}{2}\Delta I_L$$

The current limit value should be checked to ensure that  $I_{\text{LIMIT}(\text{MIN})} > I_{\text{OUT}(\text{MAX})}$ . The minimum value of current limit generally occurs with the lowest  $V_{\text{IN}}$  at the highest ambient temperature. Note that it is important to check for self-consistency between the assumed junction temperature and the resulting value of  $I_{\text{LIMIT}}$  which heats the MOSFET switches.

Caution should be used when setting the current limit based upon the  $R_{DS(ON)}$  of the MOSFETs. The maximum current limit is determined by the minimum MOSFET onresistance. Data sheets typically specify nominal and maximum values for  $R_{DS(ON)}$ , but not a minimum. A reasonable assumption is that the minimum  $R_{DS(ON)}$  lies the same amount below the typical value as the maximum lies above it. Consult the MOSFET manufacturer for further guidelines.

To further limit current in the event of a short circuit to ground, the LTC3714 includes foldback current limiting. If the output falls by more than 50%, then the maximum sense voltage is progressively lowered to about one sixth of its full value.

#### **Minimum Off-Time and Dropout Operation**

The minimum off-time  $t_{OFF(MIN)}$  is the smallest amount of time that the LTC3714 is capable of turning on the bottom MOSFET, tripping the current comparator and turning the MOSFET back off. This time is generally about 250ns. The minimum off-time limit imposes a maximum duty cycle of  $t_{ON}/(t_{ON} + t_{OFF(MIN)})$ . If the maximum duty cycle is reached, due to a dropping input voltage for example, then the output will drop out of regulation. The minimum input voltage to avoid dropout is:

$$V_{IN(MIN)} = V_{OUT} \, \frac{t_{ON} + t_{OFF(MIN)}}{t_{ON}}$$

#### **Output Voltage Programming**

The output voltage is digitally set to levels between 0.6V and 1.75V using the voltage identification (VID) inputs VID0-VID4. An internal 5-bit DAC configured as a precision resistive voltage divider sets the output voltage in increments according to Table 1. The VID codes are compatible with Intel Mobile Pentium<sup>®</sup> III processor specifications. Each VID input is pulled up by an internal 2.5 $\mu$ A current source from the INTV<sub>CC</sub> supply and includes a series diode to prevent damage from VID inputs that exceed the supply.

\*Use R<sub>SENSE</sub> value here if a sense resistor is connected between SENSE and PGND.

#### INTV<sub>CC</sub> Regulator

An internal P-channel low dropout regulator produces the 5V supply that powers the drivers and internal circuitry within the LTC3714. The  $INTV_{CC}$  pin can supply up to 50mA RMS and must be bypassed to ground with a minimum of 4.7µF tantalum or other low ESR capacitor. Good bypassing is necessary to supply the high transient currents required by the MOSFET gate drivers. Applications using large MOSFETs with a high input voltage and high frequency of operation may cause the LTC3714 to exceed its maximum junction temperature rating or RMS current rating. Most of the supply current drives the MOSFET gates unless an external EXTV<sub>CC</sub> source is used. In continuous mode operation, this current is IGATECHG =  $f(Q_{\alpha(TOP)} + Q_{\alpha(BOT)})$ . The junction temperature can be estimated from the equations given in Note 2 of the Electrical Characteristics. For example, the LTC3714EG is limited to less than 14mA from a 30V supply:

$T_J = 70^{\circ}C + (14mA)(30V)(130^{\circ}C/W) = 125^{\circ}C$

For larger currents, consider using an external supply with the  $\mathsf{EXTV}_{\mathsf{CC}}$  pin.

| VID4 | VID3 | VID2 | VID1 | VIDO | V <sub>OUT</sub> (V) |

|------|------|------|------|------|----------------------|

| 0    | 0    | 0    | 0    | 0    | 1.75V                |

| 0    | 0    | 0    | 0    | 1    | 1.70V                |

| 0    | 0    | 0    | 1    | 0    | 1.65V                |

| 0    | 0    | 0    | 1    | 1    | 1.60V                |

| 0    | 0    | 1    | 0    | 0    | 1.55V                |

| 0    | 0    | 1    | 0    | 1    | 1.50V                |

| 0    | 0    | 1    | 1    | 0    | 1.45V                |

| 0    | 0    | 1    | 1    | 1    | 1.40V                |

| 0    | 1    | 0    | 0    | 0    | 1.35V                |

| 0    | 1    | 0    | 0    | 1    | 1.30V                |

| 0    | 1    | 0    | 1    | 0    | 1.25V                |

| 0    | 1    | 0    | 1    | 1    | 1.20V                |

| 0    | 1    | 1    | 0    | 0    | 1.15V                |

| 0    | 1    | 1    | 0    | 1    | 1.10V                |

| 0    | 1    | 1    | 1    | 0    | 1.05V                |

| 0    | 1    | 1    | 1    | 1    | 1.00V                |

| 1    | 0    | 0    | 0    | 0    | 0.975V               |

| 1    | 0    | 0    | 0    | 1    | 0.950V               |

| 1    | 0    | 0    | 1    | 0    | 0.925V               |

| 1    | 0    | 0    | 1    | 1    | 0.900V               |

| 1    | 0    | 1    | 0    | 0    | 0.875V               |

| 1    | 0    | 1    | 0    | 1    | 0.850V               |

| 1    | 0    | 1    | 1    | 0    | 0.825V               |

| 1    | 0    | 1    | 1    | 1    | 0.800V               |

| 1    | 1    | 0    | 0    | 0    | 0.775V               |

| 1    | 1    | 0    | 0    | 1    | 0.750V               |

| 1    | 1    | 0    | 1    | 0    | 0.725V               |

| 1    | 1    | 0    | 1    | 1    | 0.700V               |

| 1    | 1    | 1    | 0    | 0    | 0.675V               |

| 1    | 1    | 1    | 0    | 1    | 0.650V               |

| 1    | 1    | 1    | 1    | 0    | 0.625V               |

| 1    | 1    | 1    | 1    | 1    | 0.600V               |

#### Table 1. VID Output Voltage Programming

#### EXTV<sub>CC</sub> Connection

The EXTV<sub>CC</sub> pin can be used to provide MOSFET gate drive and control power from the output or another external source during normal operation. Whenever the EXTV<sub>CC</sub> pin is above 4.7V the internal 5V regulator is shut off and an internal 50mA P-channel switch connects the EXTV<sub>CC</sub> pin to INTV<sub>CC</sub>. INTV<sub>CC</sub> power is supplied from EXTV<sub>CC</sub> until this pin drops below 4.5V. Do not apply more than 7V to the EXTV<sub>CC</sub> pin and ensure that EXTV<sub>CC</sub>  $\leq$  V<sub>IN</sub>. The following list summarizes the possible connections for EXTV<sub>CC</sub>:

1. EXTV\_{CC} grounded.  $\ensuremath{\mathsf{INTV}_{\mathsf{CC}}}$  is always powered from the internal 5V regulator.

2. EXTV<sub>CC</sub> connected to an external supply. A high efficiency supply compatible with the MOSFET gate drive requirements (typically 5V) can improve overall efficiency.

3. EXTV<sub>CC</sub> connected to an output derived boost network. The low voltage output can be boosted using a charge pump or flyback winding to greater than 4.7V. The system will start-up using the internal linear regulator until the boosted output supply is available.

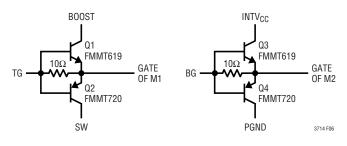

#### **External Gate Drive Buffers**

The LTC3714 drivers are adequate for driving up to about 60nC into MOSFET switches with RMS currents of 50mA. Applications with larger MOSFET switches or operating at frequencies requiring greater RMS currents will benefit from using external gate drive buffers such as the LTC1693. Alternately, the external buffer circuit shown in Figure 6 can be used. Note that the bipolar devices reduce the signal swing at the MOSFET gate, and benefit from increased EXTV<sub>CC</sub> voltage of about 6V.

Figure 6. Optional External Gate Driver

#### Soft-Start and Latchoff with the RUN/SS Pin

The RUN/SS pin provides a means to shut down the LTC3714 as well as a timer for soft-start and overcurrent latchoff. Pulling the RUN/SS pin below 1.5V puts the LTC3714 into a low quiescent current shutdown ( $I_Q \leq 30\mu A$ ). Releasing the pin allows an internal 1.2 $\mu A$  internal current source to charge up the external timing capacitor C<sub>SS</sub>. If RUN/SS has been pulled all the way to ground, there is a delay before starting of about:

$$t_{DELAY} = \frac{1.5V}{1.2\mu A} C_{SS} = (1.3s/\mu F)C_{SS}$$

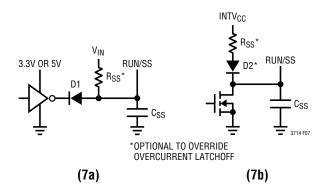

When the voltage on RUN/SS reaches 1.5V, the LTC3714 begins operating with a clamp on  $I_{TH}$  of approximately 0.9V. As the RUN/SS voltage rises to 3V, the clamp on  $I_{TH}$  is raised until its full 2.4V range is available. This takes an additional 1.3s/µF, during which the load current is folded back until the output reaches 50% of its final value. The pin can be driven from logic as shown in Figure 7. Diode D1 reduces the start delay while allowing  $C_{SS}$  to charge up slowly for the soft-start function.

After the controller has been started and given adequate time to charge up the output capacitor,  $C_{SS}$  is used as a short-circuit timer. After the RUN/SS pin charges above 4V, if the output voltage falls below 75% of its regulated value, then a short-circuit fault is assumed. A 1.7µA current then begins discharging  $C_{SS}$ . If the fault condition persists until the RUN/SS pin drops to 3.5V, then the con-

troller turns off both power MOSFETs, shutting down the converter permanently. The RUN/SS pin must be actively pulled down to ground in order to restart operation.

The overcurrent protection timer requires that the softstart timing capacitor  $C_{SS}$  be made large enough to guarantee that the output is in regulation by the time  $C_{SS}$  has reached the 4V threshold. In general, this will depend upon the size of the output capacitance, output voltage and load current characteristic. A minimum soft-start capacitor can be estimated from:

$C_{SS} > C_{OUT} V_{OUT} R_{SENSE} (10^{-4} [F/Vs])$

Generally  $0.1\mu$ F is more than sufficient.

Overcurrent latchoff operation is not always needed or desired. Load current is already limited during a shortcircuit by the current foldback circuitry and latchoff operation can prove annoying during troubleshooting. The feature can be overridden by adding a pull-up current of >5µA to the RUN/SS pin. The additional current prevents the discharge of C<sub>SS</sub> during a fault and also shortens the soft-start period. Using a resistor to V<sub>IN</sub> as shown in Figure 7a is simple, but slightly increases shutdown current. Connecting a resistor to INTV<sub>CC</sub> as shown in Figure 7b eliminates the additional shutdown current, but requires a diode to isolate C<sub>SS</sub>. Any pull-up network must be able to pull RUN/SS above the 4.5V maximum threshold that arms the latchoff circuit and overcome the 4µA maximum discharge current.

Figure 7. RUN/SS Pin Interfacing with Latchoff Defeated

#### Efficiency Considerations

The percent efficiency of a switching regulator is equal to the output power divided by the input power times 100%. It is often useful to analyze individual losses to determine what is limiting the efficiency and which change would produce the most improvement. Although all dissipative elements in the circuit produce losses, four main sources account for most of the losses in LTC3714 circuits:

1. DC I<sup>2</sup>R losses. These arise from the resistances of the MOSFETs, inductor and PC board traces and cause the efficiency to drop at high output currents. In continuous mode the average output current flows through L, but is chopped between the top and bottom MOSFETs. If the two MOSFETs have approximately the same  $R_{DS(ON)}$ , then the resistance of one MOSFET can simply be summed with the resistances of L and the board traces to obtain the DC I<sup>2</sup>R loss. For example, if  $R_{DS(ON)} = 0.01\Omega$  and  $R_L = 0.005\Omega$ , the loss will range from 15mW up to 1.5W as the output current varies from 1A to 10A for a 1.5V output.

2. Transition loss. This loss arises from the brief amount of time the top MOSFET spends in the saturated region during switch node transitions. It depends upon the input voltage, load current, driver strength and MOSFET capacitance, among other factors. The loss is significant at input voltages above 20V and can be estimated from:

Transition Loss  $\cong$  (1.7A<sup>-1</sup>) V<sub>IN</sub><sup>2</sup> I<sub>OUT</sub> C<sub>RSS</sub> f

3. INTV<sub>CC</sub> current. This is the sum of the MOSFET driver and control currents. This loss can be reduced by supplying INTV<sub>CC</sub> current through the  $EXTV_{CC}$  pin from a high efficiency source, such as an output derived boost network or alternate supply if available.

4. C<sub>IN</sub> loss. The input capacitor has the difficult job of filtering the large RMS input current to the regulator. It must have a very low ESR to minimize the AC I<sup>2</sup>R loss and sufficient capacitance to prevent the RMS current from causing additional upstream losses in fuses or batteries.

Other losses, including  $C_{OUT}$  ESR loss, Schottky diode D1 conduction loss during dead time and inductor core loss generally account for less than 2% additional loss.

When making any adjustments to improve efficiency, the final arbiter is the total input current for the regulator at your operating point. If you make a change and the input current decreases, then you improved the efficiency. If there is no change in input current, then there is no change in efficiency.

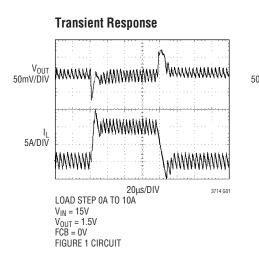

#### **Checking Transient Response**

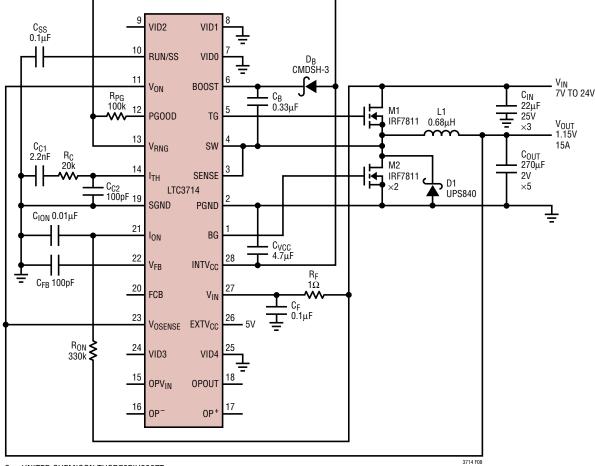

The regulator loop response can be checked by looking at the load transient response. Switching regulators take several cycles to respond to a step in load current. When a load step occurs,  $V_{OUT}$  immediately shifts by an amount equal to  $\Delta I_{LOAD}$  (ESR), where ESR is the effective series resistance of  $C_{OUT}$ .  $\Delta I_{LOAD}$  also begins to charge or discharge  $C_{OUT}$  generating a feedback error signal used by the regulator to return  $V_{OUT}$  to its steady-state value. During this recovery time,  $V_{OUT}$  can be monitored for overshoot or ringing that would indicate a stability problem. The I<sub>TH</sub> pin external components shown in Figure 8 will provide adequate compensation for most applications. For a detailed explanation of switching control loop theory see Linear Technology Application Note 76.

#### **Design Example**

As a design example, take a supply with the following specifications:  $V_{IN} = 7V$  to 24V (15V nominal),  $V_{OUT} = 1.15V \pm 100mV$ ,  $I_{OUT(MAX)} = 15A$ , f = 300kHz. First, calculate the timing resistor with  $V_{ON} = V_{OUT}$ :

$$R_{ON} = \frac{1}{(300 \text{kHz})(10 \text{pF})} = 330 \text{k}$$

and choose the inductor for about 40% ripple current at the maximum  $V_{\mbox{\scriptsize IN}}$  :

$$L = \frac{1.15V}{(300kHz)(0.4)(15A)} \left(1 - \frac{1.15V}{24V}\right) = 0.6\mu H$$

Choosing a standard value of  $0.68 \mu H$  results in a maximum ripple current of:

$$\Delta I_L = \frac{1.15V}{(300 \text{kHz})(0.68 \mu \text{H})} \left(1 - \frac{1.15V}{24V}\right) = 5.4\text{A}$$

Next, choose the synchronous MOSFET switch. Because of the narrow duty cycle and large current, a single SO-8 MOSFET will have difficulty dissipating the power lost in the switch. Choosing two IRF7811s ( $R_{DS(ON)} = 0.013\Omega$ ,  $C_{RSS} = 60$ pF) yields a nominal sense voltage of:

$V_{SNS(NOM)} = (15A)(0.5)(1.3)(0.013\Omega) = 127mV$

Tying V<sub>RNG</sub> to INTV<sub>CC</sub> will set the current sense voltage range for a nominal value of 140mV with current limit occurring at 186mV. To check if the current limit is acceptable, assume a junction temperature of about 100°C above a 50°C ambient with  $\rho_{150°C} = 1.6$ :

$$I_{\text{LIMIT}} \ge \frac{186\text{mV}}{(0.5)(1.6)(0.013\Omega)} + \frac{1}{2}(5.4\text{A}) = 20\text{A}$$

and double check the assumed  $T_J$  in the MOSFET:

$$\begin{split} \mathsf{P}_{\mathsf{BOT}} &= \frac{24\mathsf{V} - 1.15\mathsf{V}}{24\mathsf{V}} \bigg(\frac{20\mathsf{A}}{2}\bigg)^2 \big(1.6\big) \big(0.013\Omega\big) = 1.98\,\mathsf{W} \\ \mathsf{T}_\mathsf{J} &= 50^\circ\mathsf{C} + (1.98\,\mathsf{W})(50^\circ\mathsf{C}/\mathsf{W}) = 149^\circ\mathsf{C} \end{split}$$

CIN: UNITED CHEMICON THCR70EIH226ZT COUT: PANASONIC EEFUE0D271 L1: SUMIDA CEP125-4712-T007

Because the top MOSFET is on for such a short time, a single IRF7811 will be sufficient. Checking its power dissipation at current limit with  $\rho_{80^{\circ}C} = 1.2$ :

$$P_{\text{TOP}} = \frac{1.15\text{V}}{24\text{V}} (20\text{A})^2 (1.2)(0.013\Omega) + (1.7)(24\text{V})^2 (20\text{A})(60\text{pF})(300\text{kHz}) = 0.299\text{W} + 0.353\text{W} = 0.652\text{W}$$

$$T_J = 50^{\circ}C + (0.652W)(50^{\circ}C/W) = 82.6^{\circ}C$$

The junction temperatures will be significantly less at nominal current, but this analysis shows that careful attention to heat sinking will be necessary in this circuit.

$C_{IN}$  is chosen for an RMS current rating of about 6A at temperature. The output capacitors are chosen for a low ESR of  $0.005\Omega$  to minimize output voltage changes due to inductor ripple current and load steps. The ripple voltage will be only:

However, a OA to 15A load step will cause an output change of up to:

$\Delta V_{OUT(STEP)} = \Delta I_{LOAD} (ESR) = (15A) (0.005\Omega) = \pm 75 \text{mV}$ The complete circuit is shown in Figure 8.

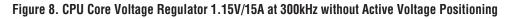

#### Active Voltage Positioning

Active voltage positioning (also termed load "deregulation" or droop) describes a technique where the output voltage varies with load in a controlled manner. It is useful in applications where rapid load steps are the main cause of error in the output voltage. By positioning the output voltage at or above the regulation point at zero load, and below the regulation point at full load, one can use more of the error budget for the load step. This allows one to reduce the number of output capacitors by relaxing the ESR requirement.

In the design example, Figure 8, five  $0.025\Omega$  capacitors are required in parallel to keep the output voltage within tolerance. Using active voltage positioning, the same specification can be met with only **three** capacitors. In this case, the load step will cause an output voltage change of:

$$\Delta V_{\text{OUT}(\text{STEP})} = (15\text{A}) \left(\frac{1}{3}\right) (0.025\Omega) = 125\text{mV}$$

By positioning the output voltage 60mV above the regulation point at no load, it will drop 65mV below the regulation point after the load step. However, when the load disappears or the output is stepped from 15A to 0A, the 65mV is recovered. This way, a total of 65mV change is observed on  $V_{OUT}$  in all conditions, whereas a total of  $\pm$ 75mV or 150mV is seen on  $V_{OUT}$  without voltage positioning.

Implementing active voltage positioning requires setting a precise gain between the sensed current and the output voltage. Because of the variability of MOSFET on-resistance, it is prudent to use a sense resistor with active voltage positioning. In order to minimize power lost in this resistor, a low value of  $0.003\Omega$  is chosen. The nominal sense voltage will now be:

$V_{SNS(NOM)} = (0.003\Omega)(15A) = 45mV$

To maintain a reasonable current limit, the voltage on the  $V_{RNG}$  pin is reduced to 0.5V by connecting it between INTV<sub>CC</sub> and GND, corresponding to a 50mV nominal sense voltage.

Next, the gain of the LTC3714 error amplifier must be determined. The change in  $I_{TH}$  voltage for a corresponding change in the output current is:

$$\Delta I_{TH} = \left(\frac{12V}{V_{RNG}}\right) R_{SENSE} \Delta I_{OUT}$$

$$= (24)(0.003\Omega)(15A) = 1.08V$$

The corresponding change in the output voltage is determined by the gain of the error amplifier and feedback divider. The LTC3714 error amplifier has a transconductance  $g_m$  that is constant over both temperature and a wide  $\pm 40$ mV input range. Thus, by connecting a load resistance  $R_{VP}$  to the  $I_{TH}$  pin, the error amplifier gain can be precisely set for accurate voltage positioning.

$$\Delta I_{TH} = g_m R_{VP} \left( \frac{0.6V}{V_{0UT}} \right) \Delta V_{0UT}$$

Solving for this resistance value:

$$R_{VP} = \frac{V_{OUT} \Delta I_{TH}}{(0.6V)g_m \Delta V_{OUT}}$$

$$= \frac{(1.15V)(1.08V)}{(0.6V)(1.7mS)(60mV)} = 20.3k$$

The gain setting resistance  $R_{VP}$  is implemented with two resistors,  $R_{VP1}$  connected from  $I_{TH}$  to ground and  $R_{VP2}$  connected from  $I_{TH}$  to  $INTV_{CC}$ . The parallel combination of these resistors must equal  $R_{VP}$  and their ratio determines

nominal value of the  $I_{TH}$  pin voltage when the error amplifier input is zero. To set the beginning of the load line at the regulation point, the  $I_{TH}$  pin voltage must be set to correspond to zero output current. The relation between voltage and the output current is:

$$I_{TH(NOM)} = \left(\frac{12V}{V_{RNG}}\right) R_{SENSE} \left(I_{OUT} - \frac{1}{2}\Delta I_L\right) + 0.75V$$

$$= \left(\frac{12V}{0.5V}\right) (0.003\Omega) \left(0A - \frac{1}{2}5.4A\right) + 0.75V$$

$$= 0.55V$$

CIN: UNITED CHEMICON THCR70EIH226ZT COUT: PANASONIC EEFUE0D271 L1: SUMIDA CEP125-4712-T007

Solving for the required values of the resistors:

$$\begin{split} R_{VP1} &= \frac{5V}{5V - I_{TH(NOM)}} \; R_{VP} = \frac{5V}{5V - 0.55V} 20.3k \\ &= 23k \\ R_{VP2} &= \frac{5V}{I_{TH(NOM)}} \; R_{VP} = \frac{5V}{0.55V} 20.3k = 185k \end{split}$$

The modified circuit is shown in Figure 9. Refer to Linear Technology Design Solutions 10 for additional information about output voltage positioning.

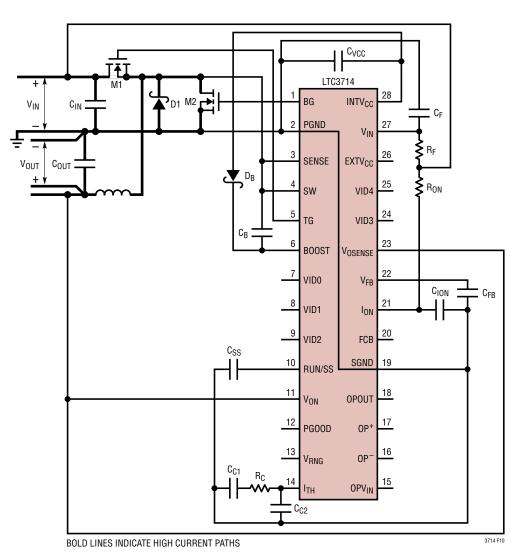

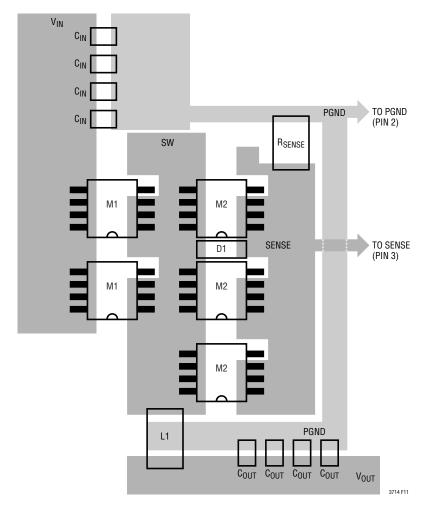

#### **PC Board Layout Checklist**

When laying out the printed circuit board, use the following checklist to ensure proper operation of the controller.

Figure 10. LTC3714 Layout Diagram

These items are also illustrated in Figures 10 and 11.

- Segregate the signal and power grounds. All small signal components should return to the SGND pin at one point which is then tied to the PGND pin close to the source of M2.

- Place M2 as close to the controller as possible, keeping the PGND, BG and SENSE traces short.

- Connect the input capacitor(s)  ${\rm C}_{\rm IN}$  close to the power MOSFETs. This capacitor carries the MOSFET AC current.

- Keep the high dV/dT SW, BOOST and TG nodes away from sensitive small-signal nodes.

- Connect the  $\mathsf{INTV}_{\mathsf{CC}}$  decoupling capacitor  $\mathsf{C}_{\mathsf{VCC}}$  closely to the  $\mathsf{INTV}_{\mathsf{CC}}$  and PGND pins.

- Connect the top driver boost capacitor  $\mathsf{C}_\mathsf{B}$  closely to the BOOST and SW pins.

- Connect the  $V_{IN}$  pin decoupling capacitor  $C_F$  closely to the  $V_{IN}$  and PGND pins.

- VID0-VID4 interface circuitry must return to SGND.

Figure 11. General Layout of External Power Components

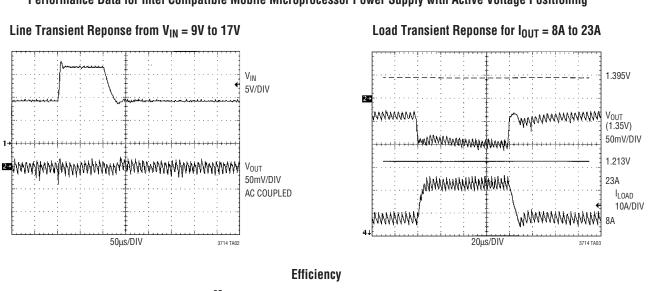

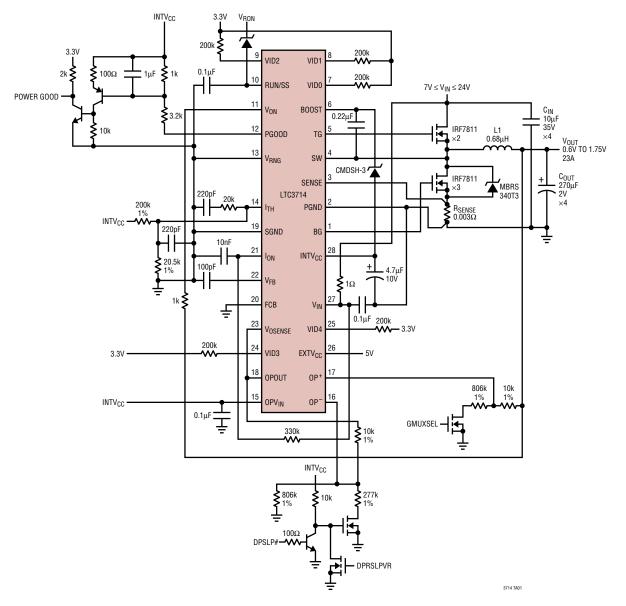

## TYPICAL APPLICATION

Performance Data for Intel Compatible Mobile Microprocessor Power Supply with Active Voltage Positioning

95 V<sub>OUT</sub> = 1.35V 90 V<sub>IN</sub> = 8.5V EFFICIENCY (%) = 15\ 'IN 85 V<sub>IN</sub> = 24V 80 75 70 0 3 6 9 12 15 18 21 LOAD CURRENT (A) 3714 TA04

### TYPICAL APPLICATION

Transmeta Crusoe<sup>™</sup> Microprocessor Power Supply with Active Voltage Positioning

## PACKAGE DESCRIPTION

**G** Package

\*DIMENSIONS DO NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED .152mm (.006") PER SIDE \*\*DIMENSIONS DO NOT INCLUDE INTERLEAD FLASH. INTERLEAD

FLASH SHALL NOT EXCEED .254mm (.010") PER SIDE

Crusoe is a trademark of Transmeta Corporation.

Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

## TYPICAL APPLICATION

Intel Compatible Mobile Microprocessor Power Supply with Active Voltage Positioning

## **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                                                       | COMMENTS                                                                                                       |  |

|-------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|

| LTC1778     | Low Duty Cycle, No R <sub>SENSE</sub> <sup>™</sup> Step-Down Controller           | SENSE <sup>™</sup> Step-Down Controller GN-16 Package, 0.8V Reference, Burst Mode Operation                    |  |

| LTC3711     | 5-Bit Adjustable, Low Duty Cycle, No R <sub>SENSE</sub> ,<br>Step-Down Controller | GN-24 Package, 5-Bit VID, 0.8V <sub>REF</sub> , Burst Mode Operation, 0.925V $\leq$ V <sub>OUT</sub> $\leq$ 2V |  |

| LTC3716     | Dual Phase, High Efficiency Step-Down Controller                                  | 2-Phase, 5-Bit VID (0.6V to 1.75V), Narrow 36-Pin SSOP, $3.5V \le V_{IN} \le 36V$                              |  |

| LTC3778     | Wide VIN, No R <sub>SENSE</sub> Step-Down Controller                              | $4V \le V_{IN} \le 36V$ , True Current Mode Control, $1A \le I_{OUT} \le 20A$                                  |  |

No  $\mathsf{R}_{\mathsf{SENSE}}$  is a trademark of Linear Technology Corporation.